電子產(chǎn)業(yè)一站式服務平臺

首頁>技術中心>搜索:串

主站蜘蛛池模板:

国产高清视频一区二区

|

欧美视频在线一区

|

亚洲欧美一区二区三区不卡

|

国产中文字幕亚洲

|

亚洲一区二区

|

黄色一级毛片a

|

精品成人免费一区二区在线播放

|

av中文字幕在线播放

|

欧美精品在线观看

|

国产专区一区

|

国产成人av在线

|

中文字幕四区

|

999国内精品永久免费视频

|

久国产精品视频

|

国产精品99久久久久久动医院

|

欧美九九九

|

天天碰天天操

|

日韩在线资源

|

久久精品久久久久电影

|

a免费在线

|

中文字幕在线观看一区二区三区

|

一级片视频在线观看

|

91精品国产亚洲

|

成人国产精品久久

|

无码日韩精品一区二区免费

|

国产成年人电影在线观看

|

日本一区二区在线播放

|

av网站在线看

|

www中文字幕

|

日韩视频中文字幕

|

91久久国产精品

|

免费的av网站

|

精品无码久久久久久国产

|

午夜精品一区二区三区在线观看

|

懂色一区二区三区av片

|

永久免费av

|

一区二区视频

|

欧美精品xx

|

亚洲 欧美 精品

|

日本中文字幕一区

|

国产精品国产

|

色综合色综合

|

午夜精品美女久久久久av福利

|

一级片欧美|

蜜桃免费视频

|

亚洲一区中文字幕在线观看

|

亚洲欧美日韩国产综合精品二区

|

亚洲国产精品成人

|

中文字幕在线免费视频

|

操批网站

|

日日久

|

久久久精品免费视频

|

天堂资源最新在线

|

中国一级特黄毛片大片

|

自拍亚洲欧美

|

欧美视频在线免费

|

久久综合激情

|

91cn国产在线

|

国产精品成人一区二区三区

|

成人午夜电影在线观看

|

羞羞动漫在线观看

|

精品国产一区二区三区免费

|

国产欧美精品一区二区三区四区

|

日日摸夜夜添夜夜添精品视频

|

亚洲毛片在线观看

|

在线视频一区二区

|

国产日韩精品久久

|

欧美日韩三级在线

|

懂色一区二区三区av片

|

在线第一页

|

午夜影院免费

|

久草免费在线

|

久久人人av

|

久久视频精品

|

黄色av大全|

sese综合

|

97色婷婷成人综合在线观看

|

亚洲一区二区三区在线免费观看

|

国产精品久久久久久亚洲调教

|

精品久久精品

|

成人欧美一区二区三区色青冈

|

青娱乐自拍偷拍

|

欧美日韩三级在线

|

国产在线网

|

午夜男人的天堂

|

特黄特黄一级片

|

亚洲第一视频网站

|

日韩一区在线播放

|

毛片免费毛片一级jjj毛片

|

色噜

|

午夜精品电影

|

成人永久免费视频

|

欧美视频一区二区

|

久久久久国产精品午夜一区

|

国产综合久久

|

久久久天堂国产精品

|

日韩资源

|

中文字幕国产日韩

|

欧美三级网址

|

色综合欧美

|

欧美日韩免费在线

|

亚洲无线看

|

国产中文在线

|

亚洲在看

|

成人欧美一区二区三区在线观看

|

国产综合精品一区二区三区

|

欧美日韩在线看

|

日本丶国产丶欧美色综合

|

亚洲国产精品99久久久久久久久

|

欧美三级在线

|

在线观看91

|

欧美黄色成人

|

国产综合久久

|

久久66|

欧美综合久久

|

欧美中文一区二区三区

|

羞羞小视频|

三级黄色片在线免费观看

|

日韩日韩日韩日韩日韩日韩

|

亚洲精品区

|

国产日产欧产美韩av

|

亚洲久久久久

|

日韩欧美第一页

|

av在线一区二区三区

|

91精品国产乱码久久久久久

|

9191国产视频

|

日韩免费看

|

91亚洲国产|

中文字幕在线不卡

|

国产日产精品一区二区三区四区

|

久久一日本道色综合久久

|

在线日韩中文字幕

|

日韩一区二区三区在线观看

|

久久中文字幕在线

|

欧美一级二级视频

|

久久久久久久

|

欧美精品一区二区三区一线天视频

|

国产特级毛片aaaaaaa高清

|

国产精品永久免费视频

|

午夜成人在线视频

|

久久久一

|

国产精品中文字幕在线观看

|

一级黄色免费网站

|

黄色一级片免费

|

观看av|

国产 欧美 日韩 一区

|

91国内视频在线观看

|

99这里只有精品视频

|

久久久亚洲精

|

91免费在线

|

亚洲精品久久久久久久久久久久久

|

午夜影院在线

|

99热在线播放

|

欧美日韩精品一区二区在线观看

|

欧美尹人

|

大片免费播放在线观看视频

|

一级录像免费录像在线观看

|

欧美区在线

|

中文在线视频

|

91在线观

|

成人美女av

|

免费观看全黄做爰大片国产

|

亚洲日韩欧美一区二区在线

|

国产精品久久久久久久久久久久久久

|

一本大道av伊人久久综合

|

欧美在线高清

|

亚洲国产精品久久久

|

国产乱码精品一区二区三区中文

|

www.99精品|

欧美亚洲视频

|

日韩午夜影院

|

欧美精品一区二区三区四区

|

欧美日韩免费在线

|

亚洲视频一区

|

亚洲狠狠

|

毛片在线网址

|

日韩欧美精品一区二区三区

|

一区免费视频

|

精品亚洲一区二区三区四区五区

|

国产精品高潮呻吟久久

|

日本做暖暖视频高清观看

|

午夜黄色影院

|

国产精品成人3p一区二区三区

|

香蕉久久久久久

|

婷婷在线视频

|

欧美在线视频不卡

|

国产日韩一区二区三区

|

欧美亚洲国产一区二区三区

|

免费看黄色一级视频

|

成人乱人乱一区二区三区

|

国产做a爰片久久毛片a我的朋友

|

91在线影院

|

91精品国产色综合久久

|

亚洲 欧美 综合

|

一区视频网站

|

久久久久久久国产

|

福利国产片

|

久久精品成人一区二区三区蜜臀

|

日本三级中文在线电影

|

国产91精品久久久久

|

日韩在线视频观看

|

亚洲精品国产一区

|

91精品国产综合久久久久久

|

亚洲精品二区三区

|

亚洲欧美一级久久精品

|

涩涩999|

欧美日韩电影一区二区三区

|

免费观看视频毛片

|

美日韩成人

|

国产在线精品一区二区

|

色综合网址

|

www.涩涩视频

|

国产精品久久久久国产a级

最新国产视频

|

国产精品毛片久久久久久久明星

|

日韩欧美综合

|

国产精品久久久久久久久久免费看

|

亚洲一区二区三区高清

|

国产欧美日韩在线观看

|

黄色小网站免费观看

|

国精产品99永久一区一区

|

在线婷婷|

亚洲日韩中文字幕一区

|

伊人春色在线播放

|

青青久草在线

|

亚洲国产精品va在线看黑人

|

蜜桃视频网站入口

|

久久精彩

|

特级a做爰全过程片

|

日韩一区中文

|

欧美大片免费高清观看

|

亚洲欧美日韩精品久久亚洲区

|

日韩成人免费中文字幕

|

欧美日韩成人在线

|

91av精品视频|

91精品国产日韩91久久久久久

|

欧洲精品二区

|

国产精品日韩欧美

|

在线观看一区三区

|

精产品自偷自拍

|

91精品一区二区三区久久久久久

|

国产精品无码久久久久

|

日韩一区二区三区在线播放

|

精品久久一区二区三区

|

久久91av|

午夜av电影

|

欧美啪啪一区二区

|

久久久综合视频

|

一区二区蜜桃

|

国产99久久精品

|

成人a视频在线观看

|

国产一区二区三区在线看

|

高清一区二区三区

|

the蜜臀av入口|

国产一区在线不卡

|

成人免费在线电影

|

91久久久久|

国产午夜精品美女视频明星a级

|

av免费人人干

|

国产亚洲精品久久久久动

|

午夜小电影

|

亚洲视频在线观看免费

|

成人免费在线视频播放

|

一级黄片毛片免费看

|

97久久精品人人做人人爽50路

|

中文日韩在线

|

日韩精品在线免费视频

|

午夜影院网站

|

天堂中文资源在线

|

ririsao久久精品一区

|

久久久久久亚洲

|

亚洲啊v

|

国产一区二区三区四

|

欧美日韩不卡合集视频

|

欧美一区二区三区在线播放

|

色综合天天天天做夜夜夜夜做

|

特黄特色大片在线观看视频网站

|

亚洲精品一二区

|

毛片一区|

中文字幕av一区二区三区

|

噜噜噜在线观看免费视频日本

|

精品欧美一区二区三区久久久

|

草久久|

一区二区三区国产在线

|

精品久久99|

极品一区

|

国产成人一级片

|

日韩一区二区三区在线观看

|

国产一区二区在线免费观看

|

欧美日韩视频一区二区

|

免费看的av|

狠狠操一区二区三区

|

51ⅴ精品国产91久久久久久

|

国产精品久久久久久

|

黄色w网站|

黄色成人av

|

91精品综合久久久久久五月天

|

国产免费一区二区三区最新6

|

毛片高清|

蜜桃av一区二区三区

|

国产一区二区在线免费观看

|

亚洲精品一区二区三区蜜桃久

|

精品一区二区av

|

日本精品中文字幕

|

免费国产一区二区

|

精品国产一二三区

|

欧美一区二区三区免费视频

|

欧美一性一交

|

亚洲一区二区三区在线

|

国产精品国产精品国产专区不片

|

日本一区二区在线视频

|

久草免费福利

|

亚洲三区电影

|

久久五月视频

|

我不卡一区|

精品第一页

|

亚洲精品在线中文字幕

|

在线中文一区

|

日韩精品极品视频在线观看免费

|

亚洲精品日本

|

久久尤物免费一区二区三区

|

欧美一级二级视频

|

国产九九九

|

欧美精品一区在线

|

激情片网站

|

精品久久久久国产

|

久久国产精品99国产精

|

成人网18免费网站

|

中文字幕在线观看日韩

|

日韩一区中文

|

动漫泳衣美女

|

久久久久久久久久久久久久av

|

国产妇女乱码一区二区三区

|

99亚洲伊人久久精品影院红桃

|

久久精品噜噜噜成人av农村

|

中文字幕一区在线观看视频

|

亚洲精选久久

|

亚洲国产成人av

|

奇米在线|

色欧美片视频在线观看

|

欧美亚洲一|

欧美午夜影院

|

一区二区三区自拍

|

久久av资源

|

色欧美片视频在线观看

|

亚洲自拍偷拍网

|

亚洲一区二区三区四区五区午夜

|

日本动漫一区

|

亚洲91精品

|

欧美成年网站

|

久草在线资源福利站

|

国产视频久久久久久久

|

久久综合久久久

|

欧美日韩中文

|

国产真实精品久久二三区

|

国产精品视频专区

|

国产综合久久久

|

久久国产精品久久久久久

|

成人午夜激情

|

亚洲精品无

|

欧美日韩美女

|

日韩欧美一区二区在线观看

|

日韩欧美在线视频

|

欧美一级黄色片免费看

|

午夜精品久久久久久久久久久久

|

这里只有久久精品

|

视频一区在线

|

亚洲精品欧美

|

国产精品美女

|

亚洲毛片

|

欧美精品亚洲

|

精品国产乱码久久久久久88av

|

伊人中文字幕

|

久久免费精品视频

|

a在线看

|

porn在线|

国产高清自拍视频

|

人人澡人人透人人爽

|

一区二区高清

|

这里只有精品久久

|

欧美一级免费

|

久久美女视频

|

国产在线在线

|

国产一级在线

|

91在线看

|

久久久久综合视频

|

成人亚洲精品777777大片

|

av在线视

|

国产一级片

|

国产成人精品免费视频大全最热

|

成人欧美一区二区三区色青冈

|

精品女同一区二区三区在线绯色

|

91在线网站

|

欧美成人一级

|

99久久精品免费

|

精品一区二区三区久久

|

亚洲一区二区三区免费观看

|

日韩免费av|

日韩av免费在线观看

|

久久国产乱|

成人免费视频008

|

国内自拍视频在线观看

|

亚洲精品久久

|

夜久久

|

av大全在线|

久久久久久亚洲一区二区三区蜜臀

|

亚色一区

|

一区二区三区四区精品

|

亚洲国产区

|

剑来在线观看

|

欧美一级免费看

|

亚洲综合无码一区二区

|

国产成人精品久久二区二区

|

欧洲成人午夜免费大片

|

色偷偷偷

|

亚洲毛片a

|

亚洲精品福利在线

|

av大片

|

婷婷五月情

|

精品国产一区二区三区忘忧草

|

国产1级片|

久久精品国产一区二区三区

|

亚洲视频一区在线播放

|

欧美在线免费观看

|

水卜樱一区二区av

|

国产99精品

|

爱色av

|

欧美在线观看一区二区

|

精品成人av

|

国产精品美女久久久久aⅴ国产馆

|

中文字幕亚洲欧美

|

人人超碰97|

欧美一级二级视频

|

男人的天堂在线免费视频

|

色吧一区|

天堂av一区

|

亚洲综合视频在线

|

日韩视频区

|

噜噜噜在线

|

欧美国产日韩精品

|

精品综合久久久

|

综合久久综合久久

|

久热久热

|

中文日韩在线

|

国产高清av在线一区二区三区

|

精品久久一区

|

中文字幕亚洲欧美日韩在线不卡

|

国产激情一区二区三区成人免费

|

99国产精品99久久久久久

|

中文字幕最新在线

|

成人av在线网

|

国产精品原创巨作av

|

国产欧美一区二区三区在线看

|

99精品网站|

国产一区二区三区视频

|

国产精品久久久久久久久费观看

|

黄色片免费观看网站

|

欧美中文字幕

|

日韩精品中文字幕在线

|

国产精品视频导航

|

日本在线观看网址

|

国产精品福利在线观看

|

亚洲aⅴ天堂av在线电影软件

|

日韩精品一区二区三区视频播放

|

天堂精品

|

国产福利一区二区三区四区

|

无码一区二区三区视频

|

99热精品免费

|

国产一区二区精品在线

|

av免费网站

|

人人澡人人透人人爽

|

日韩精品1区

|

中文字幕一区二区三区四区不卡

|

亚洲国产中文字幕

|

午夜免费福利视频

|

亚洲免费影院

|

高清中文字幕

|

日韩欧美成人影院

|

中文字幕视频在线观看

|

天天干天天射天天操

|

色.com|

中文字幕欧美激情

|

国内外成人在线视频

|

美女视频一区

|

亚洲国产欧美一区二区三区丁香婷

|

成年人黄色免费视频

|

亚洲欧美日韩精品久久亚洲区

|

日韩欧美不卡

|

黄色片小视频

|

黄色免费观看网址

|

亚洲一区二区三区高清

|

国产免费久久

|

99免费观看

|

天天综合7799精品影视

|

91网站视频在线观看

|

国产成在线观看免费视频

|

奇米久久|

国产日韩精品久久

|

久久久久久久久久久久一区二区

|

欧美久久久久

|

中文字幕免费在线观看视频

|

色视频www在线播放国产人成

|

国产日韩精品久久

|

国产综合亚洲精品一区二

|

www.国产精品|

国产精品美女久久久网av

|

欧美中文字幕一区二区三区

|

中文字幕第二十六页页

|

久久中文字幕一区二区

|

国产激情|

欧美一级片

|

成年人视频在线观看免费

|

亚洲卡一

|

久久久国产精品入口麻豆

|

免费在线黄色电影

|

国产精品区二区三区日本

|

国产第一区在线观看

|

日韩有码在线播放

|

亚洲毛片a|

亚洲国产精品一区二区第一页

|

99免费在线视频

|

3d动漫精品一区二区三区

|

成人欧美一区二区三区白人

|

狠狠操狠狠干

|

日本高清视频在线播放

|

国产91久久久久蜜臀青青天草二

|

久久视频国产

|

男女精品视频

|

国产久

|

免费看黄在线

|

伊人伊人伊人

|

亚洲午夜电影

|

精品久久久久久久久久久久久久

|

国产中文字幕亚洲

|

国产黄a三级三级看三级

|

婷婷久久五月

|

久久中文字幕一区二区三区

|

国产片在线看

|

在线色网站

|

在线欧美视频

|

亚洲精品国产二区

|

91电影院|

免费观看的av

|

免费一区二区三区

|

久久精品91|

午夜电影网址

|

玖玖国产精品视频

|

国产精品久久久久久久久久99

|

青青草草

|

亚洲欧美高清

|

在线视频自拍

|

亚洲www视频

|

成人中文视频

|

国产精品国产精品国产专区不片

|

久久久网

|

日韩精品一区二区三区四区

|

日韩码有限公司在线观看

|

亚州av一区

|

日韩在线观看视频一区二区三区

|

欧美午夜影院

|

国产精品乱码久久

|

欧美一区二区三区在线观看

|

日韩中文字幕在线视频

|

久久精品在线视频

|

国产农村妇女精品久久

|

黄色网在线看

|

日韩欧美专区

|

91 在线|

丁香综合|

国产精品视频免费

|

欧洲精品码一区二区三区免费看

|

综合久久精品

|

九一视频在线免费观看

|

久草青青|

欧美日韩视频第一页

|

一级片在线播放

|

免费观看av|

久久久久久国产精品mv

|

成人在线免费观看

|

91精品久久久久久久久久久久久久久

|

91久久精品日日躁夜夜躁国产

|

成人中文字幕在线观看

|

久久亚洲综合

|

五月激情综合

|

日韩精品一区二区三区中文在线

|

色综合视频在线

|

香蕉久久久

|

99久久毛片免费观看

|

国产日韩欧美高清

|

中文字幕在线观看第一页

|

成人免费视频在线观看

|

日本在线观看www

|

亚洲视频第一页

|

三级av在线

|

视频三区

|

91视频导航

|

亚洲高清一区二区三区

|

日韩精品一区二区三区四区五区

|

国产精品女教师av久久

|

成人一级黄色大片

|

www国产精品

|

伊人网在线|

国产在线精品一区

|

一区精品视频

|

国产精品美女久久久久aⅴ国产馆

|

爱色av网站|

极品国产在线

|

久久99操|

国产精品免费一区二区三区四区

|

欧美黄页

|

av在线免费观看网址

|

亚洲成人精品在线观看

|

午夜精品在线

|

91国内|

一区不卡

|

亚洲精品成人

|

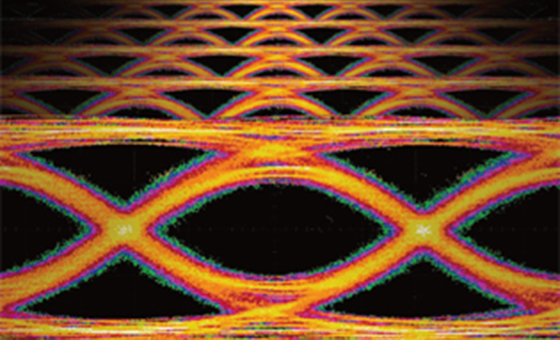

高速PCB設計中的串擾分析與控制物理分析與驗證對于確保復雜、高速PCB板級和系統(tǒng)級設計的成功起到越來越關鍵的作用。本文將介紹在信號完整性分析中抑制和改善信號串擾的方法,以及電氣規(guī)則驅(qū)動的高速PCB布線技術實現(xiàn)信號串擾控制的設計策略...

高速PCB設計中的串擾分析與控制物理分析與驗證對于確保復雜、高速PCB板級和系統(tǒng)級設計的成功起到越來越關鍵的作用。本文將介紹在信號完整性分析中抑制和改善信號串擾的方法,以及電氣規(guī)則驅(qū)動的高速PCB布線技術實現(xiàn)信號串擾控制的設計策略... 2014/09/19

2014/09/19 7099

7099 用串行RapidIO交換處理高速電路板設計的信號完整性信號完整性(SI)問題正成為數(shù)字硬件設計人員越來越關注的問題。由于無線基站、無線網(wǎng)絡控制器、有線網(wǎng)絡基礎架構(gòu)及軍用航空電子系統(tǒng)中數(shù)據(jù)速率帶寬增加,電路板的設計變得日益復雜...

用串行RapidIO交換處理高速電路板設計的信號完整性信號完整性(SI)問題正成為數(shù)字硬件設計人員越來越關注的問題。由于無線基站、無線網(wǎng)絡控制器、有線網(wǎng)絡基礎架構(gòu)及軍用航空電子系統(tǒng)中數(shù)據(jù)速率帶寬增加,電路板的設計變得日益復雜... 2014/09/16

2014/09/16 11950

11950 串行總線設計相關優(yōu)勢特點解析方案隨著目前對通信和計算機系統(tǒng)速度與帶寬的需求不斷上升,系統(tǒng)設計師正面臨著嚴峻的考驗。按時序進行測試的并行總線結(jié)構(gòu)已接近其能力的極限,總線寬度現(xiàn)達到 64位以上,致使電路布局異常復雜...

串行總線設計相關優(yōu)勢特點解析方案隨著目前對通信和計算機系統(tǒng)速度與帶寬的需求不斷上升,系統(tǒng)設計師正面臨著嚴峻的考驗。按時序進行測試的并行總線結(jié)構(gòu)已接近其能力的極限,總線寬度現(xiàn)達到 64位以上,致使電路布局異常復雜... 2014/09/16

2014/09/16 5574

5574 信號完整性——最優(yōu)化導通孔高速串聯(lián)應用?在低頻率的時候,導通孔的影響不大。但在高速系列連接中,導通孔會毀了整個系統(tǒng)。在某些情況下,在3.125Gbps的時候,他們可以采用一個樣子不錯的,寬的孔眼。在5 Gbps的時候?qū)⑺兂梢粋€支柱。了解引起導通孔限制的根本原因是優(yōu)化其設計的以及驗證他們的第一步

信號完整性——最優(yōu)化導通孔高速串聯(lián)應用?在低頻率的時候,導通孔的影響不大。但在高速系列連接中,導通孔會毀了整個系統(tǒng)。在某些情況下,在3.125Gbps的時候,他們可以采用一個樣子不錯的,寬的孔眼。在5 Gbps的時候?qū)⑺兂梢粋€支柱。了解引起導通孔限制的根本原因是優(yōu)化其設計的以及驗證他們的第一步 2014/09/15

2014/09/15 6681

6681 高速PCB板設計中的串擾問題和抑制方法 (下)信號頻率升高,上升沿越來越陡,電路板尺寸越來越小,成本要求越來越高,是當今電子設計的趨勢。尤其在消費類電子產(chǎn)品上,基本都是四層或者六層板,除去必要的電源地平面,其他層密密麻麻全走著信號。串擾也成為了一個最常見的問題

高速PCB板設計中的串擾問題和抑制方法 (下)信號頻率升高,上升沿越來越陡,電路板尺寸越來越小,成本要求越來越高,是當今電子設計的趨勢。尤其在消費類電子產(chǎn)品上,基本都是四層或者六層板,除去必要的電源地平面,其他層密密麻麻全走著信號。串擾也成為了一個最常見的問題 2014/09/06

2014/09/06 7476

7476