技術中心

減少無法加工的風險,解密生產制造,了解行業規范和術語,提升行業技能

高速高密度PCB設計面臨新挑戰隨著電子產品功能的日益復雜和性能的提高,印刷電路板的密度和其相關器件的頻率都不斷攀升,工程師面臨的高速高密度PCB設計所帶來的各種挑戰也不斷增加。除大家熟知的信號完整性(SI)問題,高速PCB技術的下一個熱點應該是電源完整性(PI)、EMC/EMI以及熱分析

高速高密度PCB設計面臨新挑戰隨著電子產品功能的日益復雜和性能的提高,印刷電路板的密度和其相關器件的頻率都不斷攀升,工程師面臨的高速高密度PCB設計所帶來的各種挑戰也不斷增加。除大家熟知的信號完整性(SI)問題,高速PCB技術的下一個熱點應該是電源完整性(PI)、EMC/EMI以及熱分析 2014-09-16

2014-09-16 6753

6753 DDR3總線信號完整性測試需要關注4點DDR總線需要測試時鐘、命令/地址、數據等,數據測試是難點,而關鍵參數是建立時間和保持時間,所以需要對讀寫信號進行分離,分離后分別測試讀和寫信號的建立時間和保持時間。

DDR3總線信號完整性測試需要關注4點DDR總線需要測試時鐘、命令/地址、數據等,數據測試是難點,而關鍵參數是建立時間和保持時間,所以需要對讀寫信號進行分離,分離后分別測試讀和寫信號的建立時間和保持時間。 2014-09-16

2014-09-16 7992

7992 特性阻抗,特性阻抗對在信號完整性中的作用和位置當信號在傳輸線上傳播時,信號感受到的瞬態阻抗與單位長度電容和材料的介電常數有關

特性阻抗,特性阻抗對在信號完整性中的作用和位置當信號在傳輸線上傳播時,信號感受到的瞬態阻抗與單位長度電容和材料的介電常數有關 2014-09-16

2014-09-16 6931

6931 高速電路設計信號完整性的一些基本概念信號完整性(Signal Integrity):就是指電路系統中信號的質量,如果在要求的時間內,信號能不失真地從源端傳送到接收端,我們就稱該信號是完整的...

高速電路設計信號完整性的一些基本概念信號完整性(Signal Integrity):就是指電路系統中信號的質量,如果在要求的時間內,信號能不失真地從源端傳送到接收端,我們就稱該信號是完整的... 2014-09-16

2014-09-16 6699

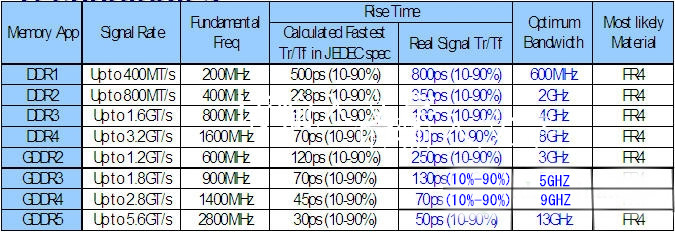

6699 高速電路設計和信號完整性分析隨著技術的進步,目前高速集成電路的信號切拘時間已經達到幾百ps,時鐘頻率也可達到幾百MHz如此高的邊沿速率導致印刷電路板上的大量互連線產生低速電路中所沒有的傳輸線效應,使信號產生失真,嚴重影響信號的正確傳輸...

高速電路設計和信號完整性分析隨著技術的進步,目前高速集成電路的信號切拘時間已經達到幾百ps,時鐘頻率也可達到幾百MHz如此高的邊沿速率導致印刷電路板上的大量互連線產生低速電路中所沒有的傳輸線效應,使信號產生失真,嚴重影響信號的正確傳輸... 2014-09-16

2014-09-16 7177

7177